# HART [HATRONICS Asynchronous Receiver/Transmitter]

### COPYRIGHT

The HATRONICS Asynchronous Receiver/Transmitter hereafter referred to as the HART, is copyrighted and all rights are reserved by HATRONICS. The distribution and sale of this hardware is intended for the use of the original purchaser only. The HART is copyrighted and all rights reserved. The HART may not, in whole or part, be copied, duplicated, reverse engineered, reproduced nor have its design altered or utilized in whole or in part, without prior consent, in writing, from HATRONICS. HART software, documentation and manuals are also copyrighted and all rights reserved. Such materials shall have all the aforementioned hardware rights and restrictions in effect.

### LIMITED WARRANTY

HATRONICS is not responsible for incidental or consequential damages resulting from breach of any express or implied warranty, including damage to property and, to the extent permitted by law, damages for personal injury. This warranty is in lieu of all other warranties or merchantability and fitness for a particular purpose..

SPECIAL THANKS TO:

ED BELL MAT DESMOND MARV SHELTON

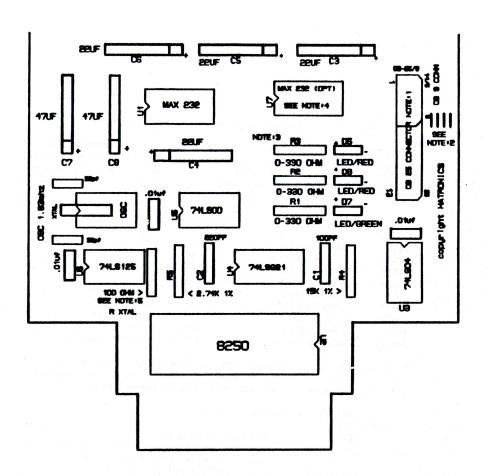

### \* PARTS PLACEMENT NOTES

## \* NOTE #1 AND 2.

THE HART PC BOARD IS DESIGNED TO ACCEPT A DB-25 CONNECTOR. TO USE A DB-25 CONNECTOR IT IS NECESSARY TO OPEN FOUR JUMPERS THAT ARE ON THE SOLDER SIDE OF THE PC BOARD. A FLAT HEAD SCREW DRIVER CAN BE USED TO BREAK OPEN THESE CONNECTION. CARE SHOULD BE TAKEN NOT TO OPEN ANY OTHER CONNECTIONS. FEMALE CONNECTORS SHOULD BE MOUNTED ON THE COMPONENT SIDE WHILE MALE CONNECTORS SHOULD BE MOUNTED ON THE SOLDER SIDE OF THE BOARD.

THE USE OF A DB-9 CONNECTOR WAS INTENDED TO BE A USABLE OPTION, BUT WAS NOT IMPLEMENTED PROPERLY DUE TO THE USE OF A MONE STANDARD MANUFACTURERS SPEC. THE PIN OUTS ARE DEFINED IN THE SOFTWARE DOCS UNDER "ASSEMBLY". TO UTILIZE A DB-9 A SPCIAL CABLE WOULD HAVE TO BE MADE. THE ON-BOARD JUMPERS THAT WERE TALKED ABOUT FOR THE DB-25 CONNECTOR MUST REMAIN INTACT.

## . NOTE #3.

RESISTERS CAN BE USED TO LIMIT THE CURRENT TO THE LEDS BUT ARE NOT MANDATORY. THESE POSITIONS CAN BE JUMPED WITH COMPONENT LEAD. THE LEDS ARE BRIGHTER WITHOUT RESISTERS.

## . NOTE #4.

THE HART CAN HAS THE MAJORITY OF THE SIGNALS NEEDED FOR A FULL RS-232 IMPLEMENTATION MINUS THE RI SIGNAL. TWO MAX 232S ARE NEEDED TO HAVE ALL THE SIGNALS ACTIVE. IF ONLY A 3 WIRE CONNECTION IS DESIRED THEN U7 DOES NOT HAVE TO BE INSTALLED. WITH U1 INSTALL THE TX,RX,RTS AND CTS SIGNALS ARE ACTIVE.

# • NOTE #5.

THERE ARE TWO BAUD RATE CLOCK OPTIONS DESIGNED INTO THE HART PC BOARD. A CRYSTAL OSC OR A CRYSTAL CAN BE INSTALLED. THE PLAN CRYSTAL WILL NEED COMPONETS R XTAL AND THO 32PF CAPS. DO NOT INSTALL THESE ADDITIONAL COMPONENTS IF A OSCILLATOR IS USED.

# HART (HATRONICS Asynchronous Receiver/Transmitter)

The HART is a deluxe, high-speed RS-232 interface designed specifically for the Commodore C-64, C-128 and C-128D computers. The HART interface is capable of sustaining interrupt driven serial-to-parallel and parallel-to-serial data conversions at spee ds in excess of 19200 baud. The HART is also FULLY PROGRAMMABLE in Commodore BASIC, 6502 and 8502 Assembler and other programming languages.

The center of the HART's design lies in the National Semiconductor NS8250A UART (Universal Asynchronous Receiver Transmitter). This is the same device that is found in the popular IBM PC, XT, AT and compatible computers. The NS8250A UART features:

- Full prioritized interrupt system controls

- o Internal diagnostic capabilities

- o Line break generation and detection

- o TRI-STATE TTL drive capabilities for bidirectional data bus

- Complete status reporting capabilities

- o False start bit detection

- Full programmable serial-interface characteristics:

- 5, 6, 7, or 8 bit characters

- even, odd, or no parity bit detection and generation

- 1, 1 1/2, or 2 stop bit generation

- baud generation

- Modem control functions (CTS,RTS,DSR,DTR,and DCD)

- Independent receiver clock input

- o Programmable baud generator

- o Independently controlled transmit, receive, and line status

- o Full double buffering

### DESIGN AND PROGRAMMING INFORMATION

Programming the HART is easy! The HART interface is connected to the Commodore computer thru the computer's cartridge port. The interface utilizes addresses 57112 (\$DF18) thru 57118 (\$DF1E) to write to the HART's internal registers, and addresses 56 856 (\$DE18) thru 56862 (\$DE1E) to read from them.

### **Memory Map**

| READ   | UART Register            | WRITE  | UART Register    |

|--------|--------------------------|--------|------------------|

| \$DE18 | Receiver Buffer          | \$DF18 | Xmiter Holding   |

| \$DE19 | Interrupt Enable         | \$DF19 | Interrupt Enable |

| \$DE1A | Interrupt Identification | SDF1A  | N/A              |

| \$DE1B | Line Control             | \$DF1B | Line Control     |

| \$DE1C | Modem Control            | \$DF1C | Modem Control    |

| \$DE1D | Line Status              | \$DF1D | Line Status      |

| \$DE1E | Modem Status             | \$DF1E | Modem Status     |

| \$DE1F | Scratch Register         | \$DF1F | Scratch Register |

|        |                          |        |                  |

The HART interface is designed to generate a user programmable NMI interrupt which can easily be used to initiate the normal Commodore NMI interrupt sequence as the following example demonstrates.

```

;NMI Initialization Routine

```

```

:NMI-init

SEI

; disable interrupts

LDA $0318

;get old ISR (interrupt service routine) address

; low-order byte. [ISR = NMI vector]

STA SOISRL

store old ISR lo-byte in OISRL

LDA $0319

;get old ISR address hi-order byte

STA SOISRH

;store old ISR hi-byte in OISRH

LDA #>NISR

;get NEW ISR lo-byte address (NISRL)

STA $0318

;store NMI low

LDA #<NISR

;get NEW ISR hi-byte address (NISRH)

STA $0319

;store NMI high

CLI

RTS

```

### :NISR

| LDA | \$DE1A    | ;read HART Interrupt Ident. Register       |

|-----|-----------|--------------------------------------------|

| CMP | #\$06     | ; check for receiver line status interrupt |

| BEQ | \$rls-svc | ;service receiver line status interrupt    |

| CMP | #\$04     | ; check for received data avail. interrupt |

| BEQ | \$rda-svc | ;service received data avail. interrupt    |

| CMP | #\$12     | ; check for character timeout interrupt    |

| BEQ | \$cti-svc | ;service character timeout interrupt       |

| CMP | #\$02     | ; check for xmit hld reg. empty interrupt  |

| BEQ | \$thr-svc | ;service xmit hld reg. empty interrupt     |

| CMP | #\$00     | ; check for modem status interrupt         |

| BEQ | \$mst-svc | ;service modem status interrupt            |

| JMP | \$01SRL   | ;service normal CBM interrupts             |

|     |           |                                            |

The HART can also be easily programmed in CBM 'native' BASIC, simply by applying the same technique to the BASIC PEEK and POKE statements. (sample code may be included elsewhere).

### MISCELLANEOUS INFORMATION:

The HART interface has been tested on C-128 computers using 1571, 1581, 1764, 1700 and 1750 commodore peripherals with NO noticeable conflicts or problems. The HART interface is powered directly by the CBM computer and requires no additional power supply.

# HART Technical Reference Information

| Read   | UART Register            | Write  | UART Register       |

|--------|--------------------------|--------|---------------------|

|        |                          |        |                     |

| \$DE18 | Receiver Buffer          | \$DF18 | Transmitter Holding |

| \$DE19 | Interrupt Enable         | \$DF19 | Interrupt Enable    |

| \$DE1A | Interrupt Identification | \$DF1A | N/A                 |

| \$DE1B | Line Control             | \$DF1B | Line Control        |

| \$DE1C | Modem Control            | \$DF1C | Modem Control       |

| \$DE1D | Line Status              | \$DF1D | Line Status         |

| \$DE1E | Modem Status             | \$DF1E | Modem Status        |

| \$DE1F | Scratch Register         | \$DF1F | Scratch Register    |